微信公众号:芯片之家(ID:chiphome-dy)

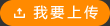

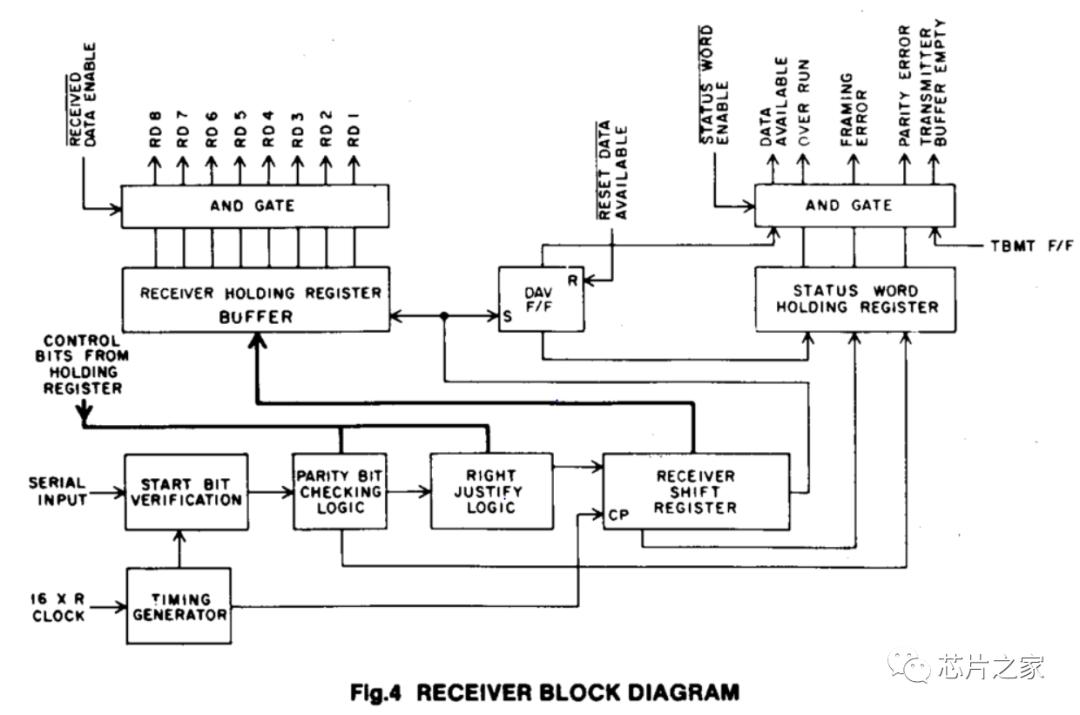

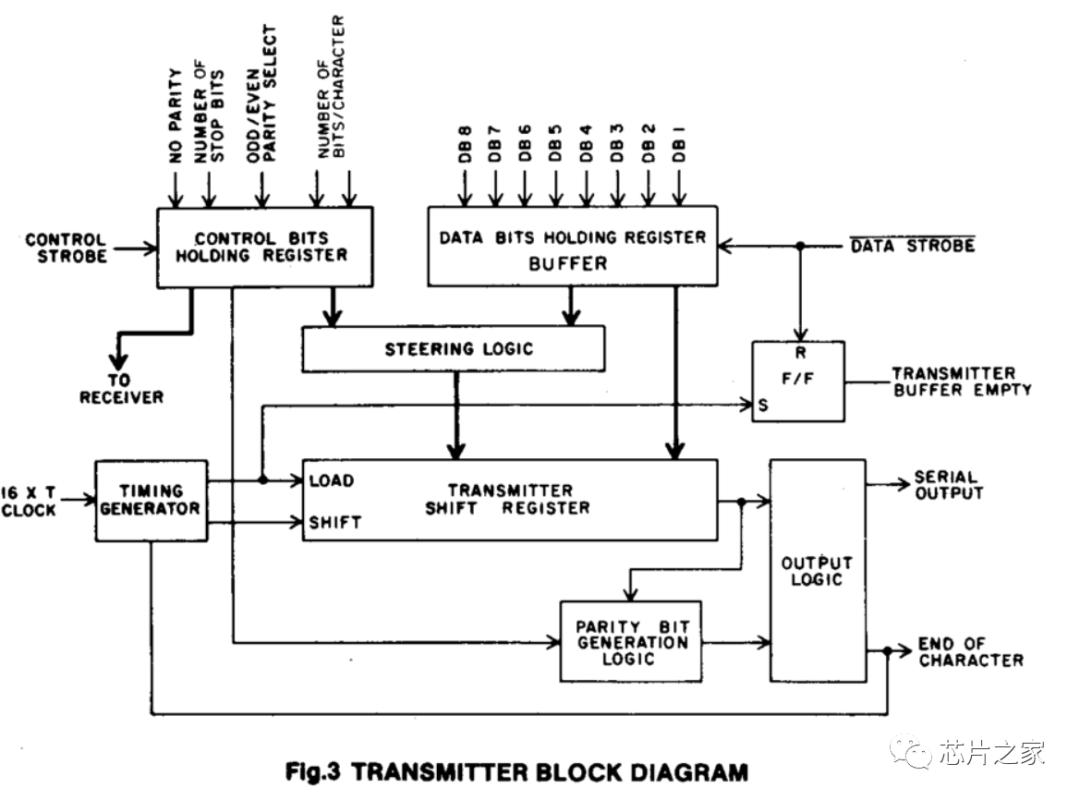

40引脚DIP封装,宽度为0.6英寸:按照当今的标准,这是是一个巨大的封装。它的内部是一个串行端口,波特率高达30k。这确实非常快,因为连接到PDP-11的终端(例如VT-52)可以最多只能运行9600波特。

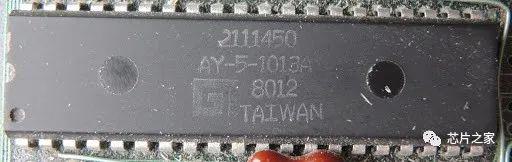

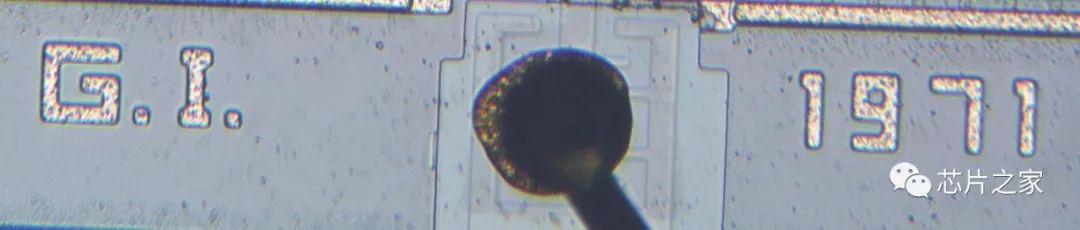

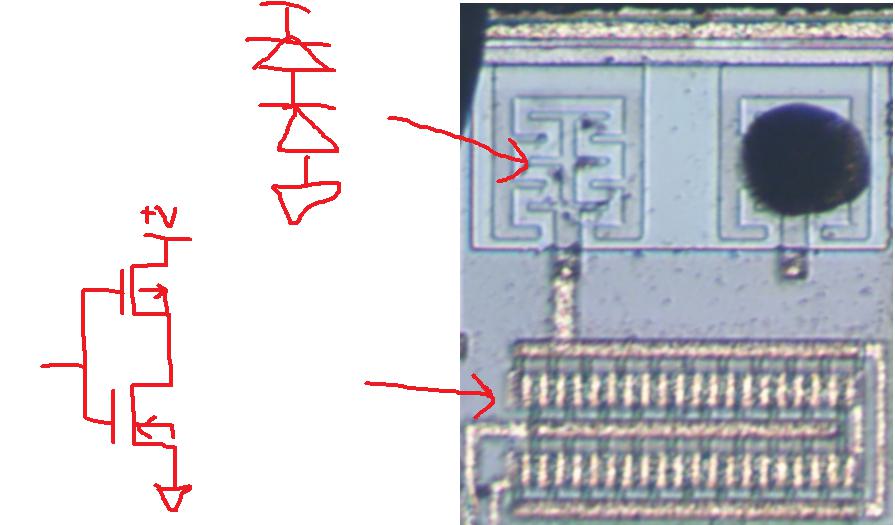

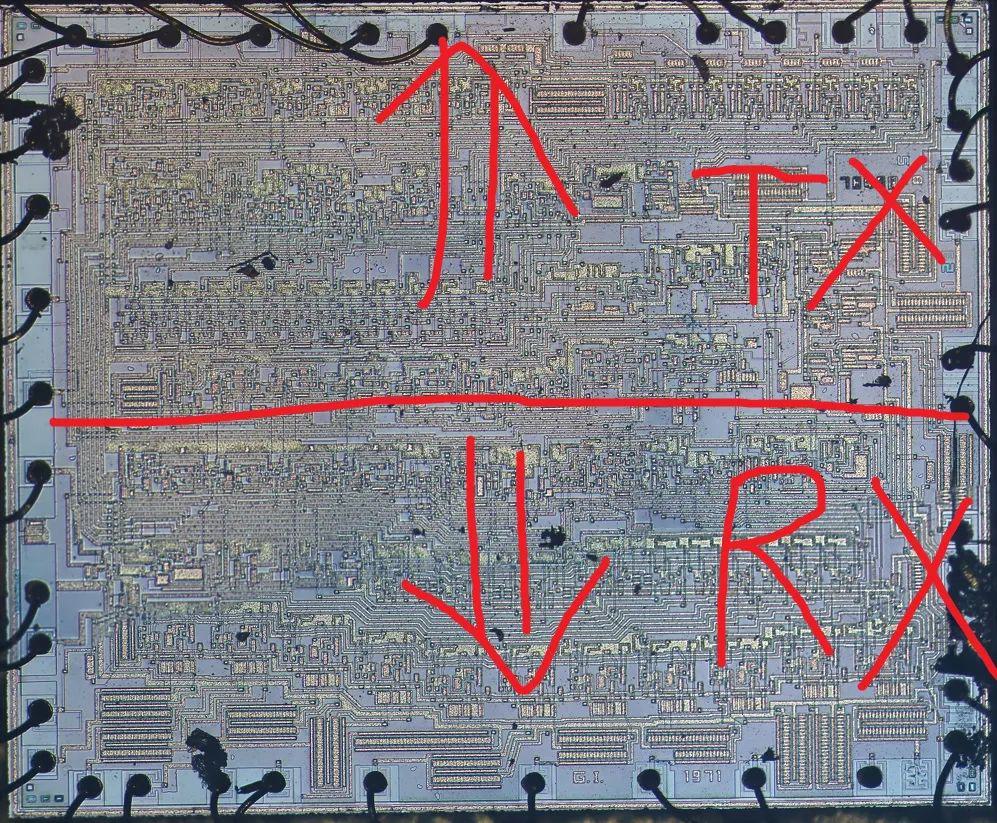

拆开包装可以看到1970年代早期技术的一个令人愉快的例子:这是中等规模的集成电路。设计该芯片时,微处理器正处于发展的边缘。就晶体管数量而言,这是当时最新的技术。

注意东西看起来像是手工放置和手绘。那时还没有自动化工具!一段有趣的历史。

请各位粉丝支持下,点赞留言并转发下朋友圈,谢谢大家了!您的转发就是我最佳创作的动力

推荐阅读

▼

电子漫画系列,更新九张图片。

电子漫画系列,更新九张图片。

【最强干货】618个3D封装免费分享

【最强干货】618个3D封装免费分享

【干货第二波】一大波3D封装免费分享

【干货第二波】一大波3D封装免费分享

贴片电容国内外品牌

贴片电容国内外品牌

DC-DC电源芯片国内外品牌大汇总

DC-DC电源芯片国内外品牌大汇总

几毛钱的32768晶振,这也能写出一篇干货?

几毛钱的32768晶振,这也能写出一篇干货?

车牌识别控制板原理图+PCB+3D齐全无私分享

车牌识别控制板原理图+PCB+3D齐全无私分享

【视觉盛宴】你没见过的电子元器件的另一面!

【视觉盛宴】你没见过的电子元器件的另一面!

完全由C编写,高度可移植,超级牛逼的菜单架构!

完全由C编写,高度可移植,超级牛逼的菜单架构!

【视频】老外教你三极管和MOS管的通电效应,我就不信还有不懂的!

【视频】老外教你三极管和MOS管的通电效应,我就不信还有不懂的!